307 VLSI Design Lab, 3rd Floor SIT,

IIT Delhi, New Delhi 110016 (India)

I am a PhD Student (since 2019) and Prime Minister Research Fellow (since 2020) in Amar Nath and Shashi Khosla School of Information Technology (SIT) at Indian Institute of Technology Delhi. I work with the Memory and embedded Architecture Research Group (MARG) headed by Prof. Preeti Ranjan Panda. I have done my Bachelors in Electronics and Communication Engineering from National Institute of Technology Allahabad. I have worked as a Design Engineer in Qualcomm Design Center, Bangalore for 3 years. Before joining PhD, I have worked as a Research Engineer in the Green IC Group led by Prof. Massimo Alioto in National University of Singapore for a year.

My broad interests lie in the field of Heterogeneous System Architecture, System design and hardware for Machine Learning. Specifically my current research focus is on Heterogeneous System-On-Chip design with Machine Learning Accelerators.

I spend my spare time reading books, listening to soft music, crafting and coloring. I am also a volunteer for NGO that goes by the name GirlsWhoCode (Globally) and SheCodesIndia. I also love traveling and meeting new people.

Department: Amar Nath and Shashi Khosla School of Information Technology Research Interests: Computer Architecture, System-on-Chip, AI Accelerators Advisor: Preeti Ranjan Panda

Performance Architecture Group, MCU/MPU Engineering

Project: Request Arbitration in Last-Level CachesIntelligent bandwidth partitioning at Last-Level Cache

Paper

Green IC Group Deep Learning Architectures

SoC Front End Design Group RTL design and Implementation of Network-On-Chip for Qualcomm MSM and MDM devices

Automatic Validation of NoC RTL-Performance Analysis

Bachelors in Electronics and Communication Engineering CGPA: 9.65/10

I am currently working on Hardware for Machine Learing running on Edge Devices. I am also working on Heterogeneous SoC design with domain-specific accelerators. Custom hardware-based neural network accelerators have been known to surpass their general-purpose processor equivalents in terms of both throughput and energy-efficiency. On-chip inference on edge devices for IOT and other AI applications has also gained traction. I am looking into application-tailored accelerators co-designed with efficient network training models and their efficient integration on edge-devices.

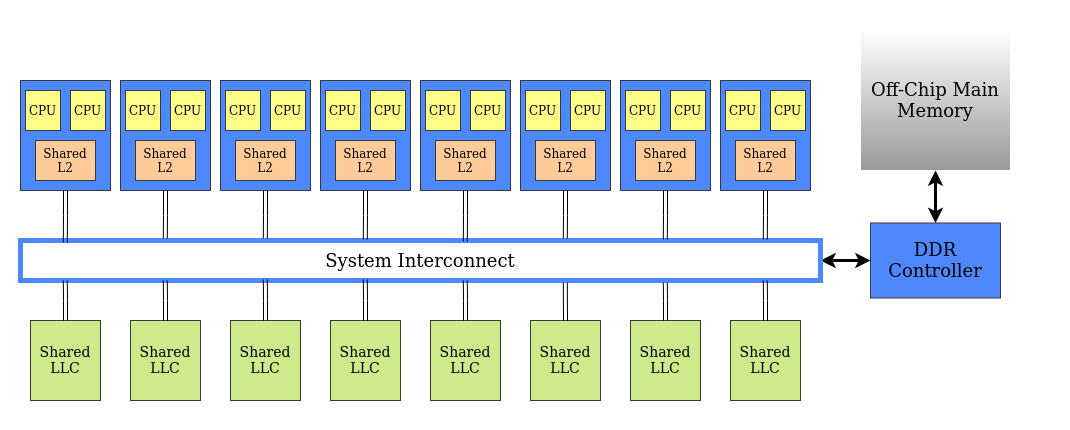

Target System Architecture

The figure depicts a system with multiple clusters of processor cores with private L1 and dual-core shared L2 caches. All the processors share a last-level cache. The last-level cache is usually banked and is connected to the DRAM controller by a system interconnect. These kind of architectures are commonly used in edge devices. Our work focuses on system-level issues occuring because of running machine learning applications on these systems. These applications are compute and memory intensive and are extremely demanding of the shared resources of the system.

Seldom the performance of other applications running on the system is affected at the cost of high performance requirement of these applications. Since more and more of these models are being run on edge devices, there is a need to understand the system-level issues mostly at the shared system resources to improve the complete system performance instead of focussing on application centered performance.

Year: 2019-2020

Year: 2020-2021

Role as a Teaching Assistantship includes defining the lab exercises, assisting students with doubts and lab work and assistance provided in evaluation.

| Year | Semester 1 | Semester 2 |

|---|---|---|

| 2019-2020 | COL 719: Synthesis of Digital Systems | COL 216: Computer Architecture |

| Taught By: Prof. Preeti Ranjan Panda | Taught By: Prof. Preeti Ranjan Panda | |

| 2020-2021 | COL 215: Digital Logic and System Design | TA off |

| Taught By: Prof. Anshul Kumar | ||

| 2021-2022 | COL 215: Digital Logic and System Design | COL 216: Computer Architecture |

| Taught By: Prof. Vireshwar Kumar and Prof. M Balakrishnan |

Taught By: Prof. Anshul Kumar | |

| 2022-2023 | COL 215: Digital Logic and System Design | COL 719: Synthesis of Digital Systems |

| Taught By: Prof. Preeti Ranjan Panda | Taught By: Prof. Preeti Ranjan Panda |

IEEE Journal on Emerging and Selected Topics in Circuits and Systems (IEEE JETCAS)

Year: 2018, 2019

IEEE Embedded System Letters (IEEE ESL)

Year: 2020, 2021, 2022, 2023

Design, Automation and Test in Europe Conference (DATE)

Year: 2021

Design Automation Conference (DAC)

Year: 2021, 2022

Asia and South Pacific Design Automation Conference (ASP-DAC)

Year: 2022

VLSI Design Conference (VLSID)

Year: 2023

ACM Transactions on Design Automation of Electronic Systems (TODAES)

Year: 2023

International Conference on Compilers, Architectures, and Synthesis for Embedded Systems (Embedded Systems Week: CASES)

Year: 2023

Prime Minister Research Fellowship, May 2020. (PMRF Webpage)

Selected for receiving the prestigious Prime Minister Research Fellowship offered by Ministry of Human Resource Development (MHRD), Government of India, from May 2020

Cadence Tensilica Hackathon at VLSI Design Conference 2019. (Pictures)

Won the first prize in the Cadence Tensilica Hackathon with team-mates Anupam Sobti and Saurabh Tewari

Institute Gold Medal 2014

Awarded the Institute Gold Medal for being the institute topper in Electronics and

Communication Engineering, 2014

Late (Dr.) Malay Raj Mukherjee Gold Medal 2014

Awarded the Late (Dr.) Malay Raj Mukherjee Gold Medal for standing first amongst the students of

B.Tech (Electrical Engineering), B.Tech (Computer Science and Engineering) and

B.Tech (Electronics and Communication Engineering)

OPJEMS scholarship 2012

Awarded the O.P. Jindal Engineering and Management scholarship by Jindal Steel and Power Ltd. for

exhibiting outstanding competency, leadership and communication skills.

Book that I have read and would like to share

People will forget my name but my voice will echo long after I perish!

"Be a rainbow in someone else's cloud" - Heartfulness

307 VLSI Design Lab, 3rd Floor SIT,

IIT Delhi, New Delhi 110016 (India)